### Welcome to

#### Conference

January 28–30, 2025 Santa Clara Convention Center

#### Expo

January 29-30, 2025

# Delta-L Measurement Analysis: Extending PCB Trace Insertion Loss Measurements to 67 GHz

James Drewniak Clear Signal Solutions, Inc.

james.drewniak@clearsig.com

#### Contributors

- Xiaoning Ye Intel

- Richard Zai PacketMicro

- Giorgi Tsintsadze Missouri S&T EMC Laboratory (now at Cisco)

- John Cheng PacketMicro

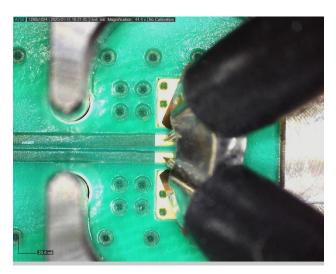

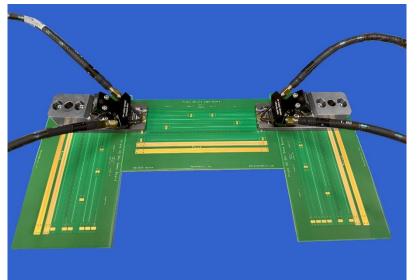

### Delta-L 4.0 Methodology – to 40 GHz

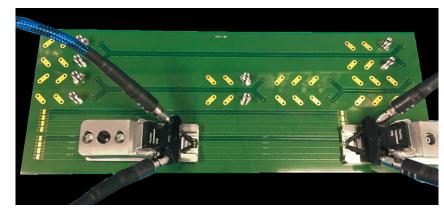

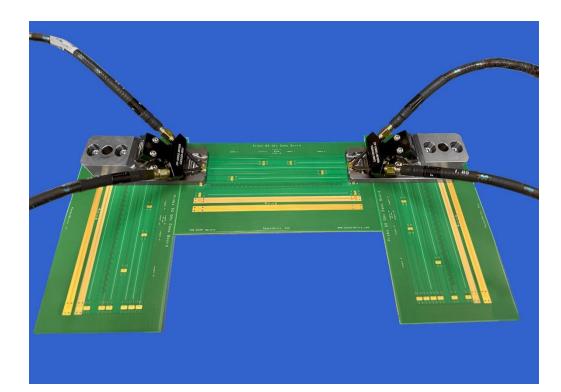

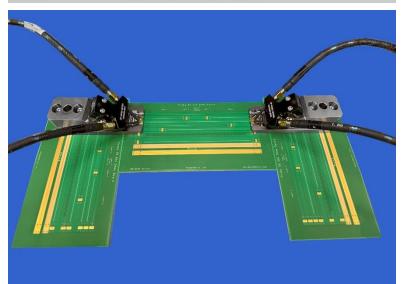

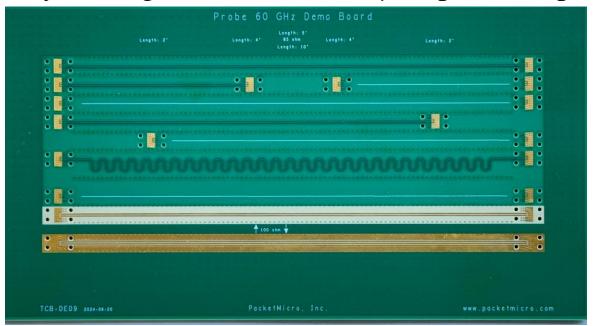

#### 2", 5", 10" trace lengths used for IL extraction

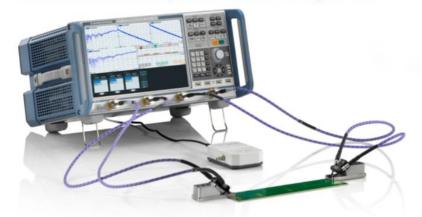

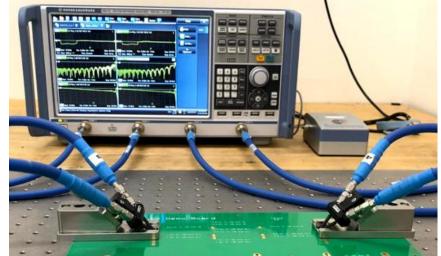

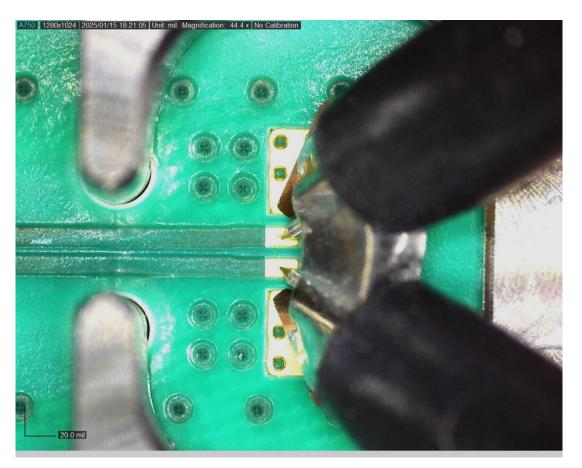

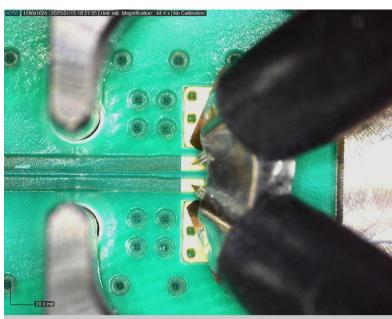

Test Vehicle with PacketMicro Probes and Bases

Universal Probe Launch with PacketMicro Probes

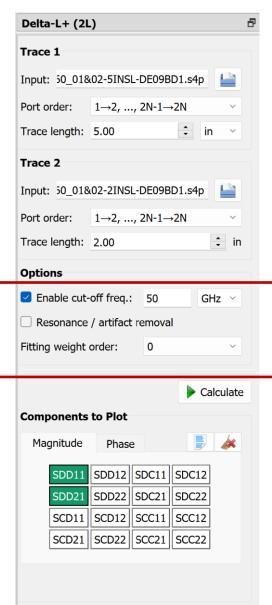

### Workflow Implemented in Commercial Toolsets

#### R&S®ZNB40 setup with Delta-L 4.0 probes

#### Delta-L Workflow for 2L on R&S®ZNB40

#### **Advanced Interconnect Test Tool (AITT) – DLP (Clear Signal Solutions)**

### Next Step – Delta-L to 67 GHz

- Want to achieve 56 GHz over 1 lane for 224 Gbps data rate/PAM4, PCIE gen 7 128 GT/s over 1 lane

- Need to achieve 67 GHz for Delta-L method

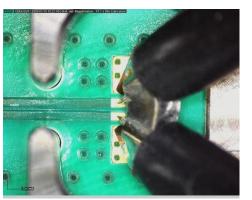

- using hand-held probes for use in large-volume measurements and in fabrication environment

- Must have a universal footprint to accommodate handheld probes and rapid alignment/placement

- 0.4 mm most likely a minimum probe pitch for rapid alignment due to manufacturing tolerance in PCB fab

- Must have trace pattern lengths for Delta-L to meet IEEE 370 STD for de-embedding accuracy e.g., 1" & 4", 2" & 5"?

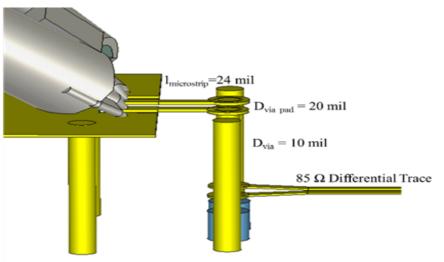

#### Delta-L 4.0 (to 40 GHz) Solution

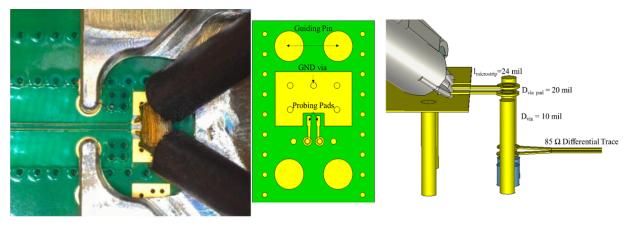

#### Universal Probe Launch with PacketMicro Probes

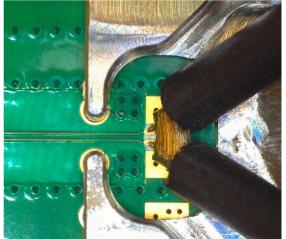

### Probing Solution to 67 GHz

- Optimize probe and via transition simultaneously to achieve a RL>6dB at 67 GHZ

- Achieve an IL < 6 dB at 67 GHz by using shorter 2X Thru

PacketMicro GSSG probe Booth 1155

### Status – PacketMicro Probes

#### Probe properties:

- 0.5 mm pitch

- GSSG configuration

- 3-mil robust probe tips

- 47-mil Coaxial cable

- 1.85mm Samtec connector

- Stainless base

PacketMicro GSSG probe

Booth 1155

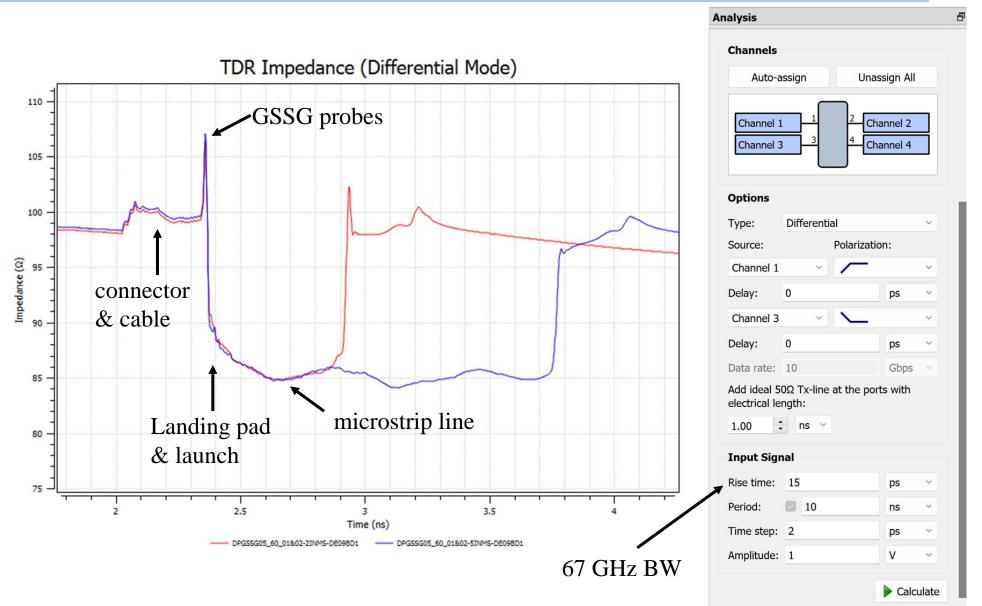

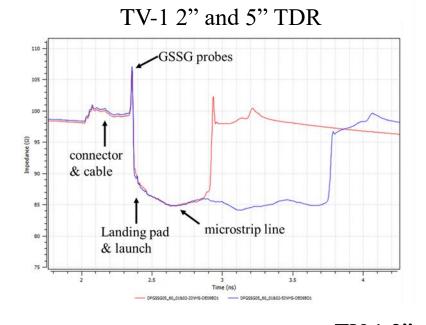

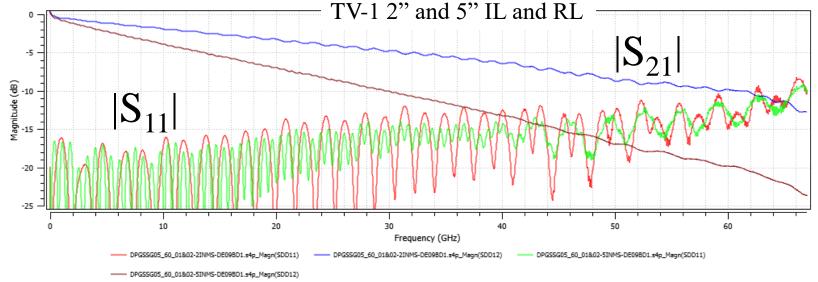

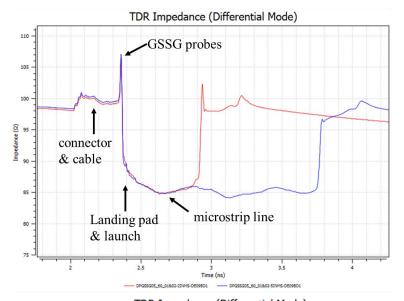

## Status – 67 GHz GSSG Probes on Microstrip - TDR

### Status – 67 GHz GSSG Probes on Microstrip – Delta-L

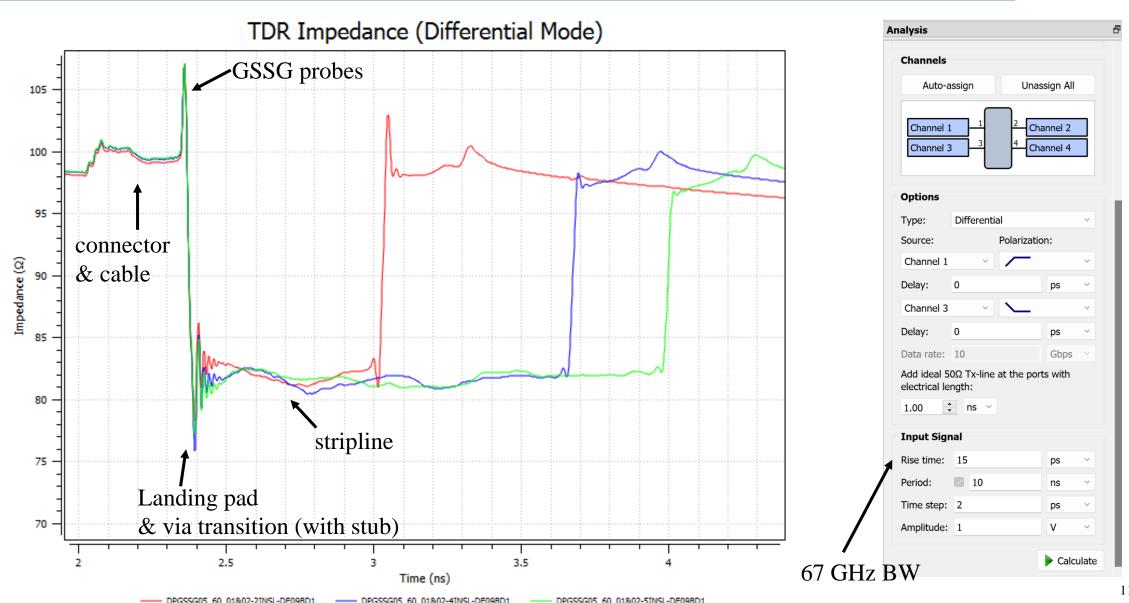

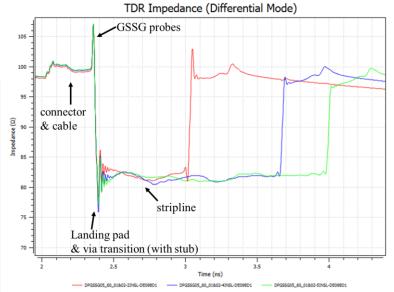

### Status – 67 GHz GSSG Probes on Stripline – TDR

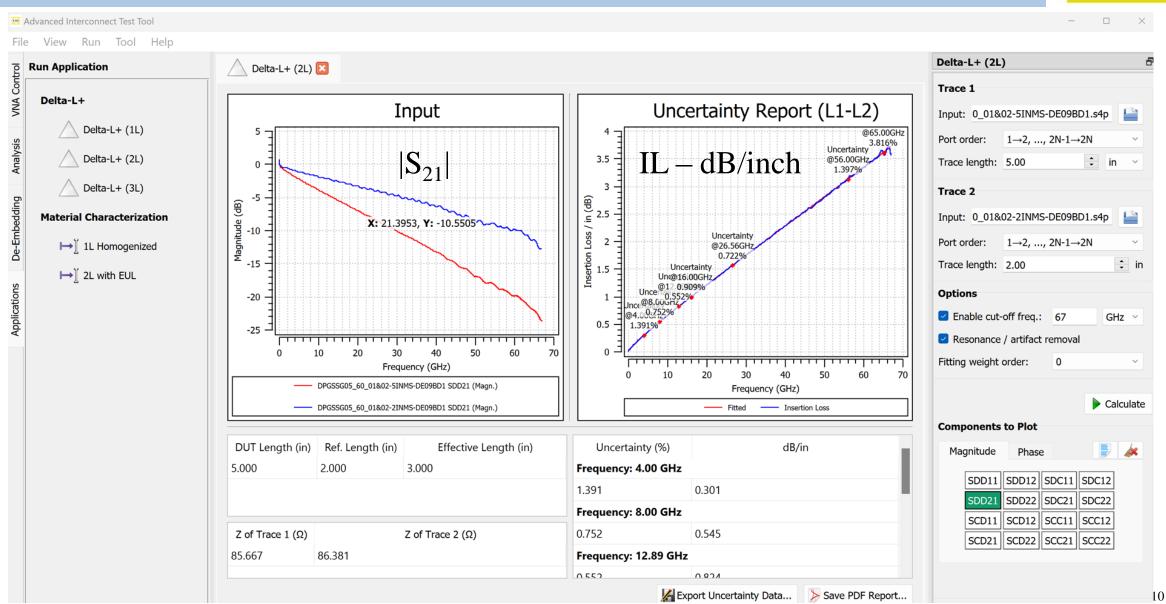

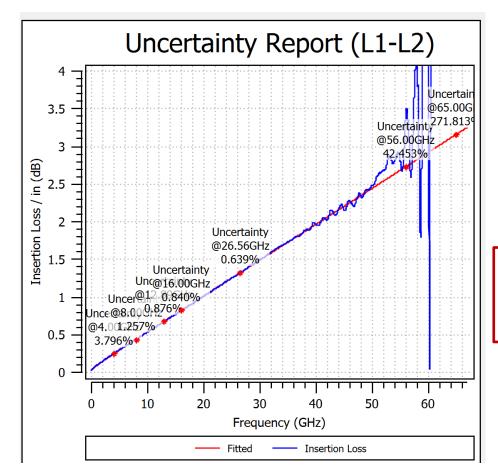

## Status – 67 GHz GSSG Probes on Stripline – Delta-L

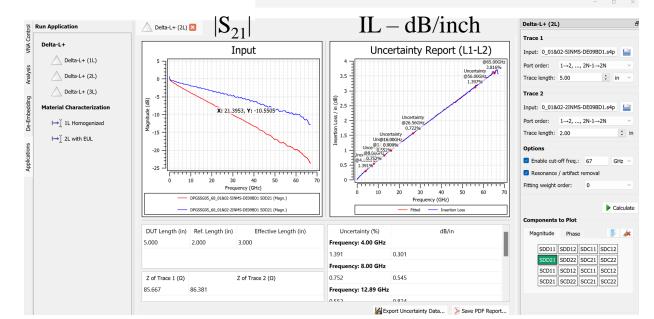

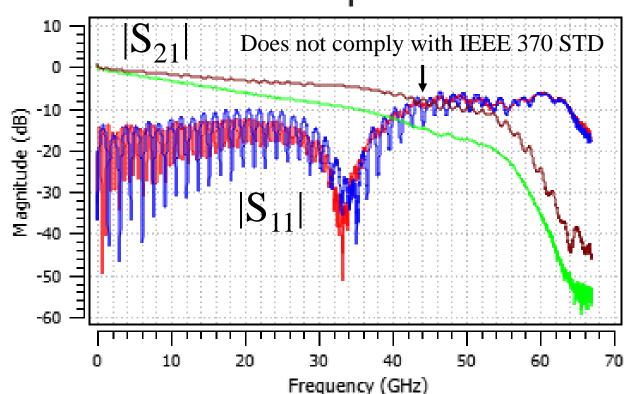

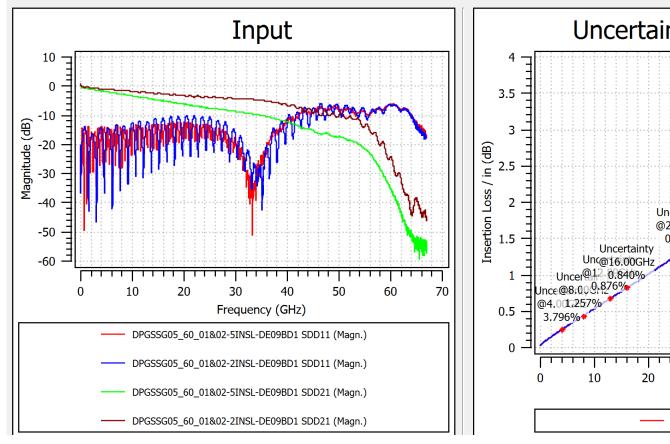

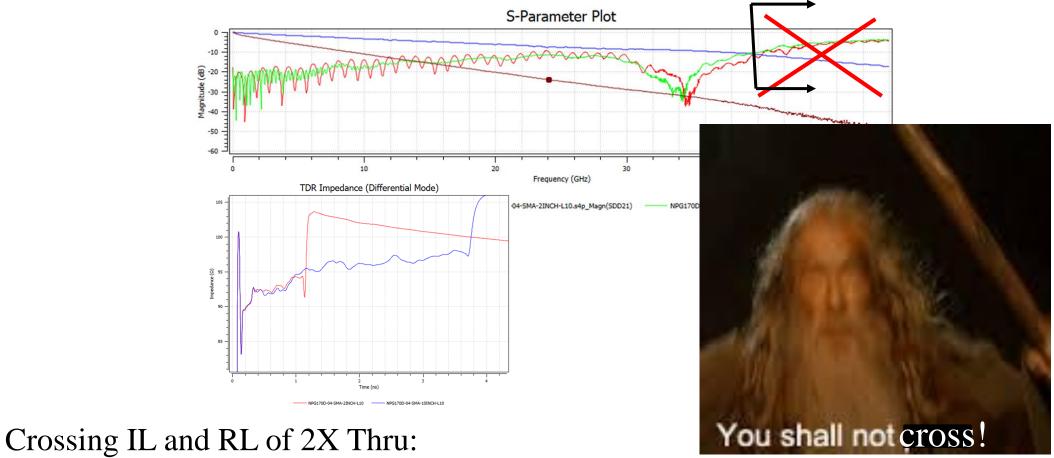

### Input

- RL and IL for 2X thru cross at 44 GHz and does not comply with IEEE 370

- Via transition not optimized and has a remaining via stub

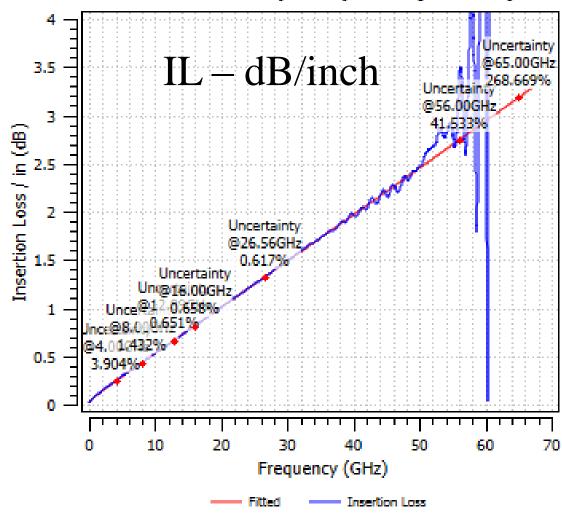

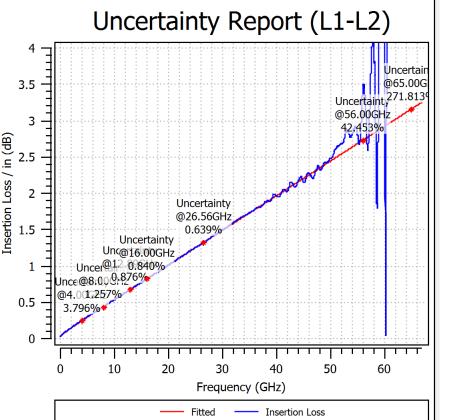

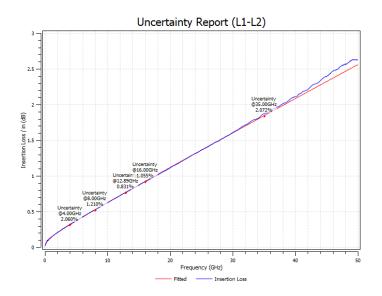

### Uncertainty Report (L1-L2)

### Outline

- The Intel Delta-L Methodology

- Test methodology

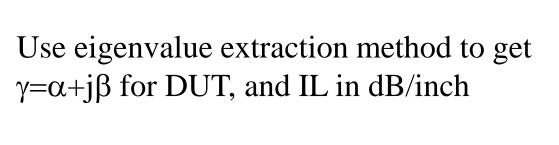

- Eigenvalue de-embedding

- Curve-fitting insertion loss

- Design and de-embedding essentials for achieving a high-quality outcome at high-frequencies

- Some essentials

- Making accurate S-parameter measurements

- Determining the reference plane for high-quality de-embedding

- causality/passivity

- Mitigating design and layout artifacts in the curve-fitting for IL

- 67 GHz Delta-L

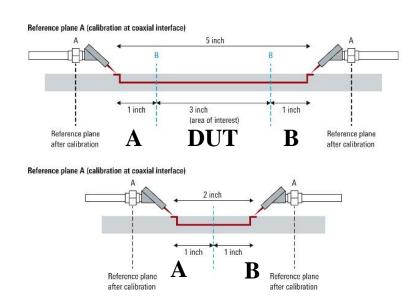

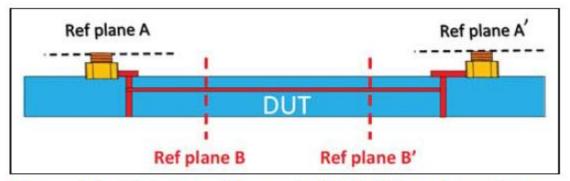

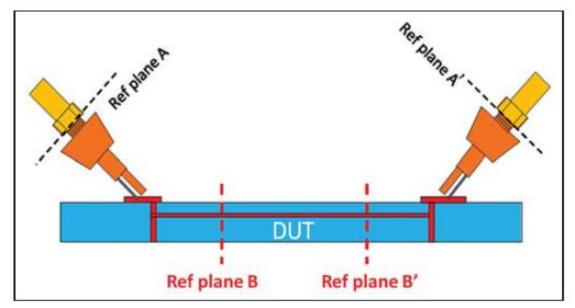

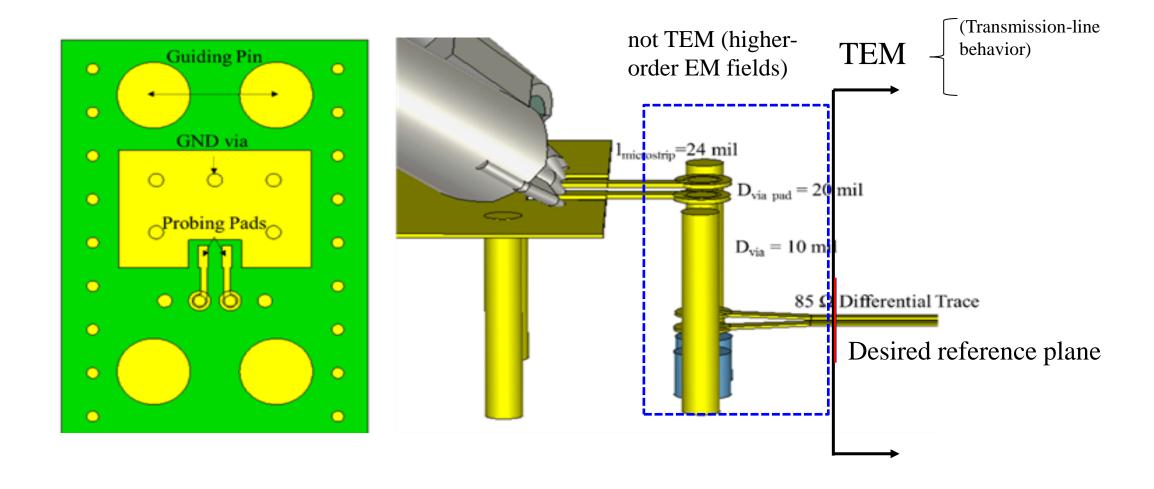

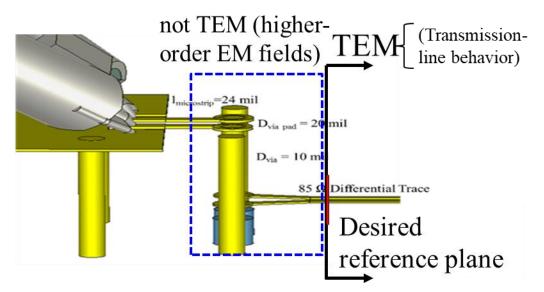

#### Delta-L References Planes

Figure 1-1 Reference Planes in Printed Board Insertion Loss Characterization

Figure 1-2 Reference Planes in Printed Board Insertion Loss Characterization with Microwave Probe

Reference planes in all cases are TEM because they are at transmission-line planes

### Eigenvalue De-embedding Method

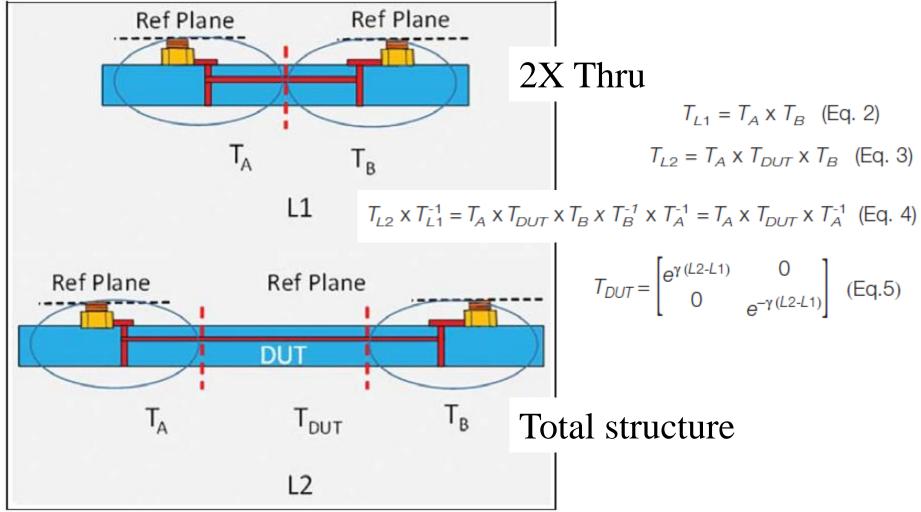

Figure 1-3 Two-line Structure for Eigenvalue-based Method

#### Calculation of Insertion Loss

$$T_{L1} = T_A \times T_B \quad \text{(Eq. 2)}$$

$$T_{L2} = T_A \times T_{DUT} \times T_B \quad \text{(Eq. 3)}$$

$$T_{L2} \times T_{L1}^{-1} = T_A \times T_{DUT} \times T_B \times T_B^{-1} \times T_A^{-1} = T_A \times T_{DUT} \times T_A^{-1}$$

(Eq. 4)

$$T_{DUT} = \begin{bmatrix} e^{\gamma (L2-L1)} & 0 \\ 0 & e^{-\gamma (L2-L1)} \end{bmatrix}$$

(Eq.5)

$T_{L2} \times T_{L1}^{-1}$  and  $T_{DUT}$  have the same eigenvalues.

Choose eigenvalue with absolute value <1 and real part is the attenuation.

Convert T-parameters to S-parameters:

$$S_{DUT} = \left[ \frac{0}{e^{-\gamma L}} \frac{e^{-\gamma L}}{0} \right]$$

(Eq.1)

$$\gamma$$

= propagation constant =  $\sqrt{(R + j\omega L)(G + j\omega C)}$  =  $\alpha + j\beta$

$$\alpha \Rightarrow$$

attenuation  $20\log_{10}(\alpha) \times length = IL$

### Case 4 – Delta-L Outcome

Delta-L+ (2L)

Input: 50\_01&02-5INSL-DE09BD1.s4p

Trace 1

- IL from eigenvalue de-embedding

- Fitted IL curve according to  $lL_{dB}(f) = a(f f_0)^b + c(f f_0)^2 + d(f f_0) + lL_0$

| Port order:                                | 1→2,, 2                                   | 2N-1→2         | 2N                   |       | ~       |  |  |  |

|--------------------------------------------|-------------------------------------------|----------------|----------------------|-------|---------|--|--|--|

| Trace length:                              | 5.00                                      |                | •                    | in    | ~       |  |  |  |

| Trace 2                                    |                                           |                |                      |       |         |  |  |  |

| Input: 50_01&02-2INSL-DE09BD1.s4p          |                                           |                |                      |       |         |  |  |  |

| Port order:                                | 1→2,, 2                                   | 2N-1→2         | 2N                   |       | ~       |  |  |  |

| Trace length:                              | 2.00                                      |                |                      | •     | in      |  |  |  |

| Options                                    |                                           |                |                      |       |         |  |  |  |

| Enable cut-                                | off freq.:                                | 50             |                      | GHz   | ~       |  |  |  |

| Resonance / artifact removal               |                                           |                |                      |       |         |  |  |  |

| Fitting weight order: 0                    |                                           |                |                      |       |         |  |  |  |

| ricting weight                             | oracii                                    | •              |                      |       |         |  |  |  |

| Tituing weight                             | orderi                                    |                |                      | C-1   | 1-1-    |  |  |  |

|                                            |                                           | J              | •                    | Calcu | ılate   |  |  |  |

| Components                                 |                                           |                |                      | Calcu | ulate   |  |  |  |

|                                            |                                           |                |                      | Calcu | ulate   |  |  |  |

| <b>Components</b> Magnitude                | to Plot                                   |                |                      |       | ulate   |  |  |  |

| Components  Magnitude  SDD11               | to Plot<br>Phase                          | DC11           | SDC1                 | 2     | ulate   |  |  |  |

| Components  Magnitude  SDD11  SDD21  SCD11 | to Plot Phase  SDD12 SI SDD22 SI SCD12 SC | DC11 DC21 CC11 | SDC1<br>SDC2<br>SCC1 | 2 2 2 | ulate   |  |  |  |

| Components  Magnitude  SDD11  SDD21  SCD11 | to Plot Phase  SDD12 SI SDD22 SI          | DC11 DC21 CC11 | SDC1<br>SDC2<br>SCC1 | 2 2 2 | ulate & |  |  |  |

| Components  Magnitude  SDD11  SDD21  SCD11 | to Plot Phase  SDD12 SI SDD22 SI SCD12 SC | DC11 DC21 CC11 | SDC1<br>SDC2<br>SCC1 | 2 2 2 | ulate 🗽 |  |  |  |

Note that above 50 GHz the de-embedding (blue curve) is becoming sensitive

## Delta-L 4.0 Curve-Fitting

$$IL_{dB}(f) = a(f - f_0)^b + c(f - f_0)^2 + d(f - f_0) + IL_0$$

Conductor loss,

including surface

roughness

IPC-TM-650TEST METHODS MANUAL, 2.5.5.14

- f<sub>0</sub> and IL<sub>0</sub> are introduced as offsets to accommodate typical 10 MHz starting points for VNA measurements

- For a perfectly smooth conductor b=0.5

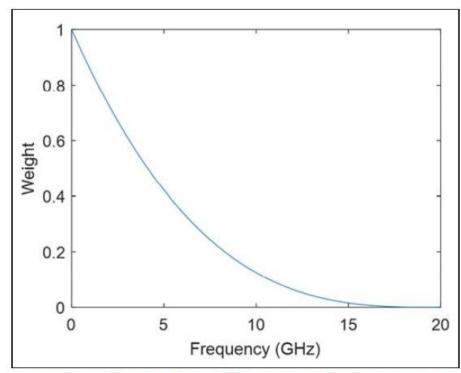

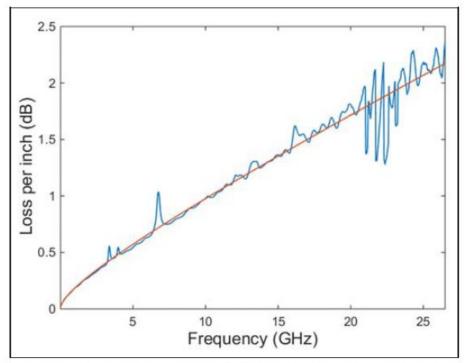

## Weighting Factor for Curve-Fitting – IPC TM-650 2.5.5.14

$$W(f) = \left(1 - \left(\frac{f}{f_{max}}\right)\right)^3 \quad (Eq.9)$$

Figure 5-3 The Suggested Weight Function for Insertion Loss Curve Fitting

Figure 5-2 Least Squares Fit Based on (eq. 7) Applied to a Representative Insertion Loss Curve

Note 1. Red represents the fitted curve.

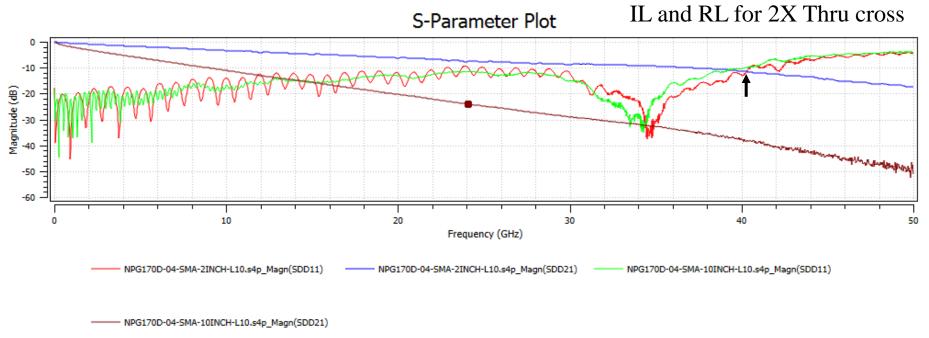

### Case 4 – 2X Thru Meeting IEEE 370 STD to 40 GHz

- The IL (blue) and RL (red) for the 2X Thru 2 in. stripline cross at 40 GHz

- The 2X Thru does not meet the IEEE 370 STD above and expect the de-embedding in Delta-L to become sensitive above 40 GHz with possibly resulting artifacts in the Delta-L 4.0 fit

Table 4—Fixture electrical requirement summary for mixed-mode interconnects

| Metric                                                       | Structure | Equation                                                                                                                       | Class A limit | Class B limit | Class C limit |

|--------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|

| Insertion loss<br>(FER1)                                     | 2X-Thru   | $20 \times \log_{10} \left  S_{DD21} \right $                                                                                  | -10 dB        | −15 dB        | −15 dB        |

| Return loss<br>(FER2)                                        | 2X-Thru   | $20 \times \log_{10}  S_{DD11} $                                                                                               | -20 dB        | -10 dB        | -6 dB         |

| Difference<br>between insertion<br>and return loss<br>(FER3) | 2X-Thru   | $ \begin{array}{c c} 20 \times \log_{10} \left  S_{DD21} \right  \\ -20 \times \log_{10} \left  S_{DD11} \right  \end{array} $ | 5 dB          | 0 dB          | 0 dB          |

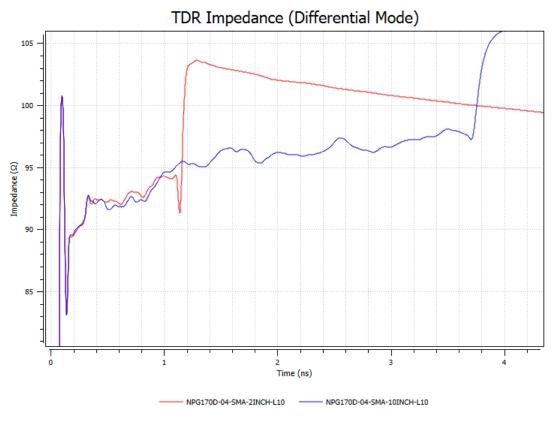

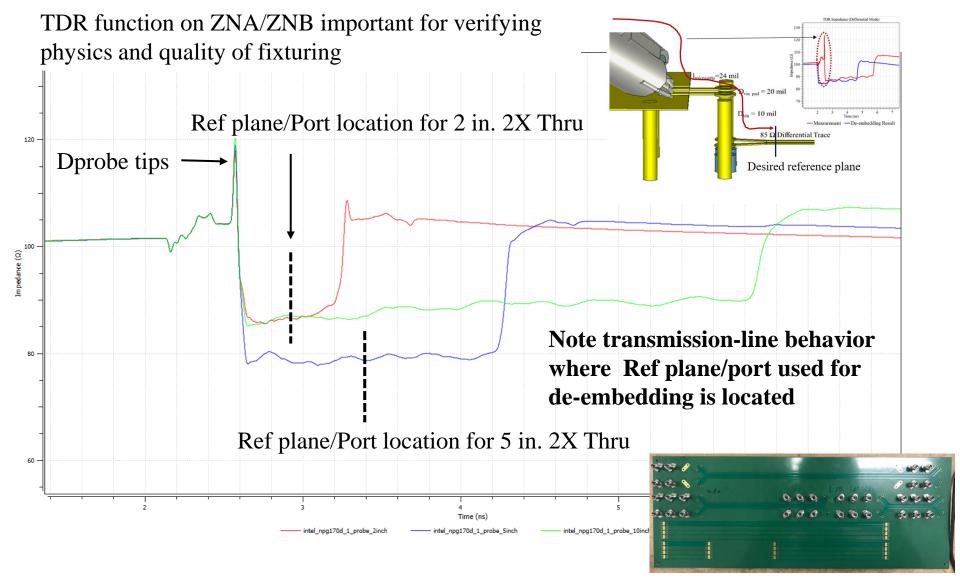

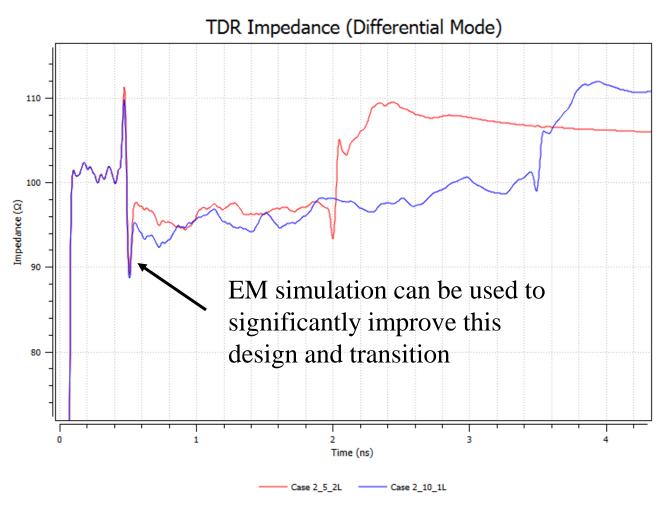

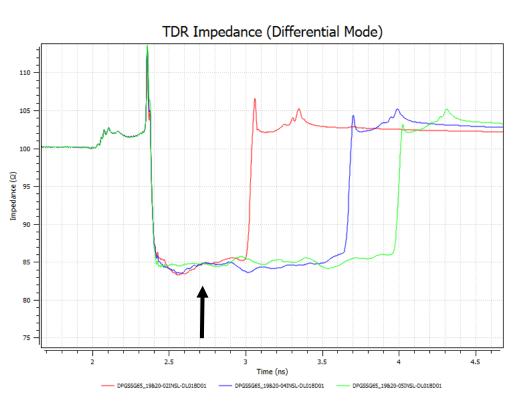

### Case 4 – TDR

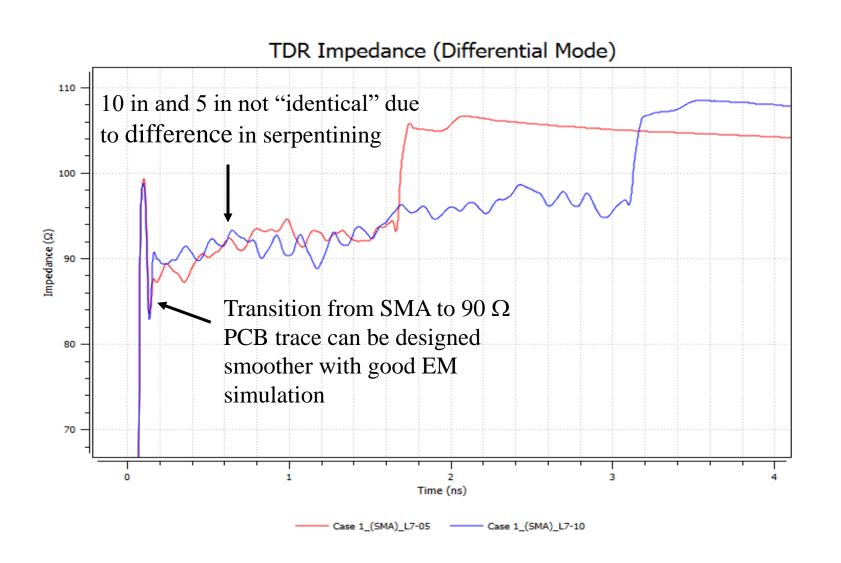

- The 2 in. and 10 in. traces are nearly identical in the transition and along the length. Will lead to better deembedding and Delta-4.0 outcome.

- The transition from  $100 \Omega$  to  $85 \Omega$  is well engineered, but the stripline impedance target of  $85 \Omega$  was missed in manufacturing. If target were hit, Delta-L 4.0 outcome to 50 GHz would have been excellent.

#### De-Embedding is Sensitive when RL and IL of 2X Thru Cross

- 2X Thru is too long and IL is higher

- Transition from connector or probes not optimized resulting in higher RL at high frequencies.

- Missed line impedance of design in manufacturing

### Outline

- The Intel Delta-L Methodology

- Test methodology

- Eigenvalue de-embedding

- Curve-fitting insertion loss

- Design and de-embedding essentials for achieving a high-quality outcome at high-frequencies

- Some essentials

- Making accurate S-parameter measurements

- Determining the reference plane for high-quality de-embedding

- causality/passivity

- Mitigating design and layout artifacts in the curve-fitting for IL

- 67 GHz Delta-L

## Making Accurate S-parameter Measurements

- Suitable high-frequency cables with precision connectors and precision adapters that are clean, maintained and not worn

- Have a mechanically stable measurement setup and avoid movement of cables and the DUT plan the layout (make good use of "painter's tape to secure cables and test fixtures)

- Proper calibration coefficients for the cal kit

- Only the connector nut should be moving when mating a connector pair.

- Use proper torque wrenches

- Warm up the VNA per manufacturer's specs before calibrating and measuring

- Calibrate the VNA immediately prior to measurements

- Use cal kits with care they are relatively fragile, and regularly have them re-characterized per specs

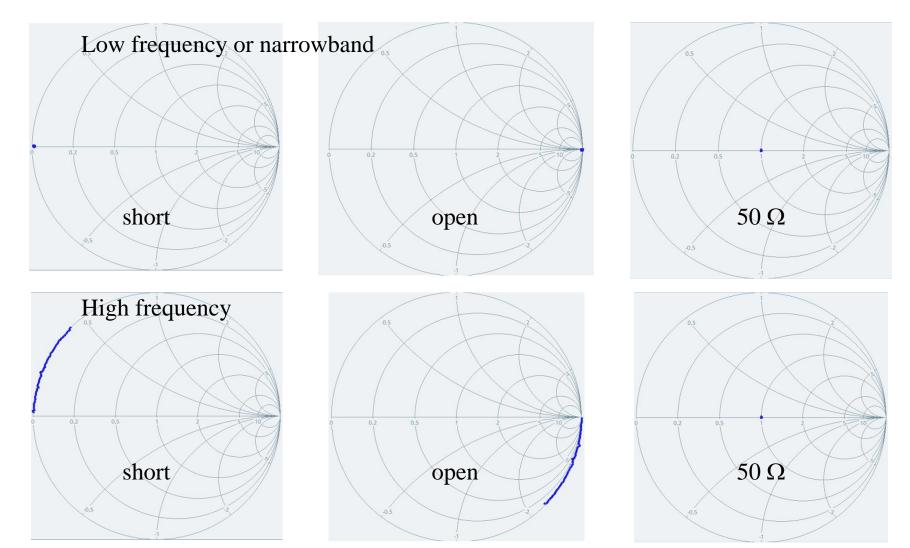

### Sanity Checks for Calibration

• Put the calibration standards back on and view on the Smith Chart to ensure that short, open, and load calibrations are "true"

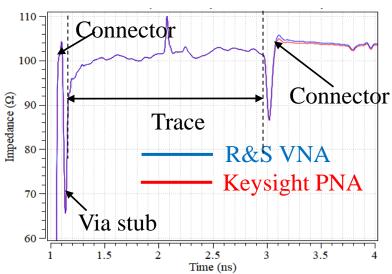

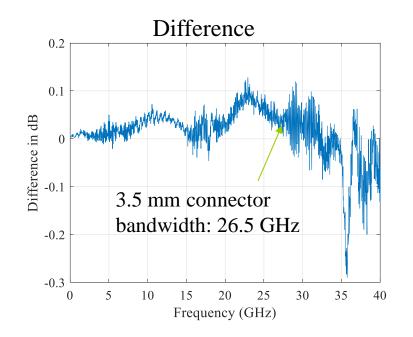

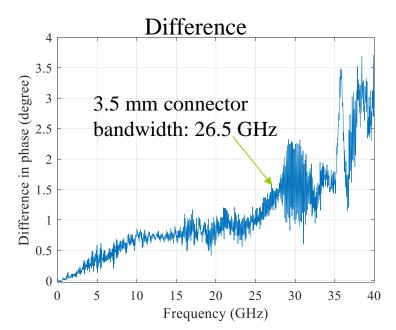

### Comparison of Two Different Vendor VNAs

Rohde & Schwarz ZNB 40 (100KHz – 40GHz)

Two adaptors are used, a 2.4 M to 3.5 F, and a 3.5M to 3.5 M.

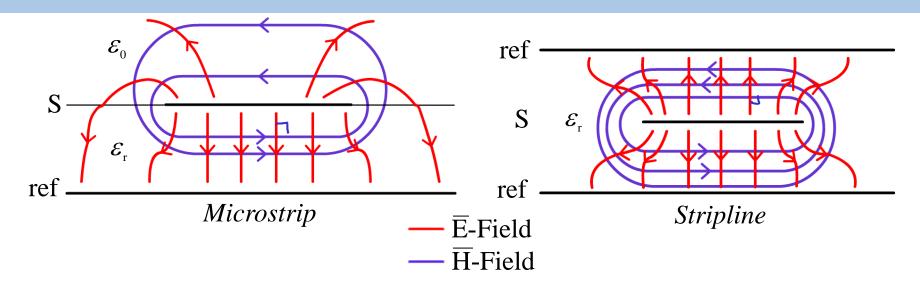

## TEM – Transverse Electromagnetic Propagation

- Transverse Electromagnetic (TEM) waves have the electric- and magnetic-field lines perpendicular, and E x H is in the direction of propagation.

- The geometry for a TEM transmission-line is translationally invariant, i.e., at every point along the length of the propagation, the cross-section geometry is the same

- TEM waves have the property that the wave speed is the same for all frequencies (no dispersion for the ideal lossless case R = G = 0).

- Stripline supports a <u>pure</u> TEM wave (though PCB stripline is technically not pure TEM, but quasi-TEM), but microstrip is <u>quasi-TEM</u>.

## TEM Boundary for Probing

### TDR for 2", 5", 10" for 85 $\Omega$ Differential Pair

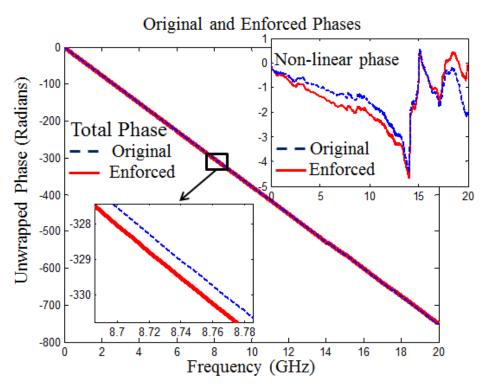

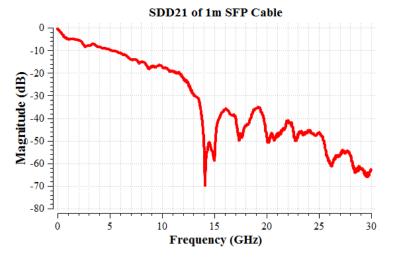

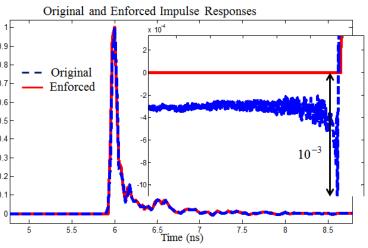

### S-Parameters—Causality and Passivity Check—IEEE 370 STD

<u>Causality</u> and <u>passivity</u> should always be checked for S-parameters. (functionality provided in AITT)

- Measured 1m SFP cable

- Maintain magnitude and enforce phase for causality, or <u>re-measure</u>

### Outline

- The Intel Delta-L Methodology

- Test methodology

- Eigenvalue de-embedding

- Curve-fitting insertion loss

- Design and de-embedding essentials for achieving a high-quality outcome at high-frequencies

- Some essentials

- Making accurate S-parameter measurements

- Determining the reference plane for high-quality de-embedding

- causality/passivity

- Mitigating design and layout artifacts in the curve-fitting for IL

- Moving toward 67 GHz Delta-L

## Layout and Artifacts

- Layout features can cause artifacts and resonances

- Long serpentine traces leads to resonances

- Insufficient ground vias at signal layer transitions can lead to a parallel-plate resonance that couples to the stripline being measured

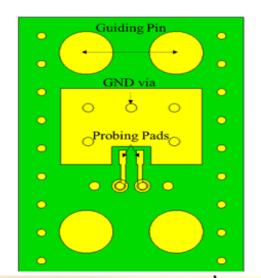

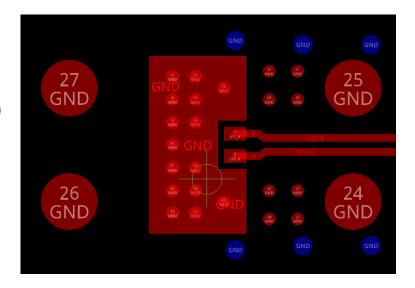

### Best practices

- Straight traces (at 67 GHz shorter traces will be necessary anyway and save space)

- Universal footprint that ensures good signal return (GND) at the via transition –

development underway at Intel/PacketMicro/Clear Signal Solutions

- Adequate ground stitching at via transition (this is part of the universal probe launch)

- No via stubs

- Via stitching that is randomized around a nominal spacing

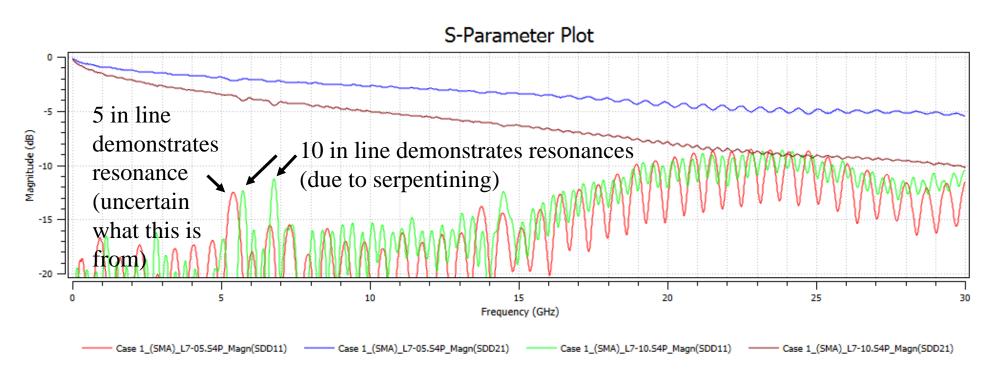

### Case 1 – Resonances Due to Serpentining: S-Parameters

- S-parameter data shows that design of transition to PCB from an SMA is fairly good

- S-parameter data meets IEEE 370 STD for de-embedding

- Resonances in data will be reflected in de-embedding and must be dealt with in loss fitting

### Case 1 – Differential TDR

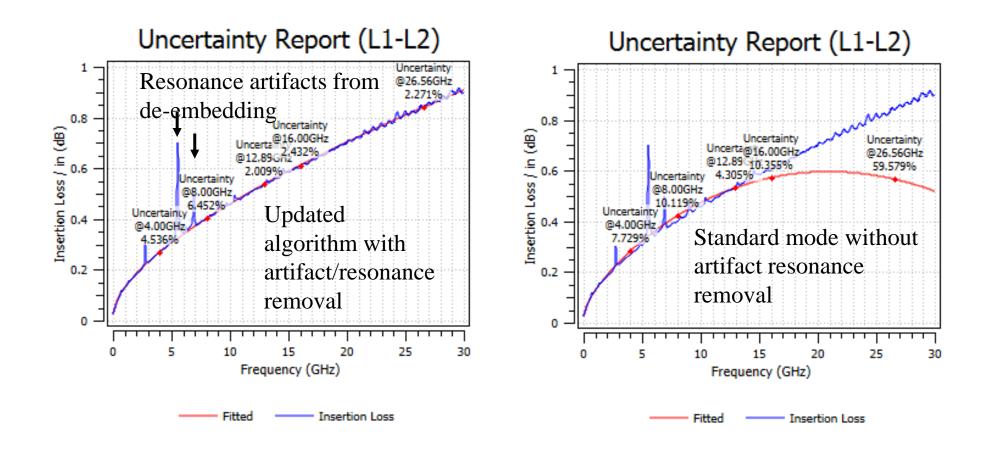

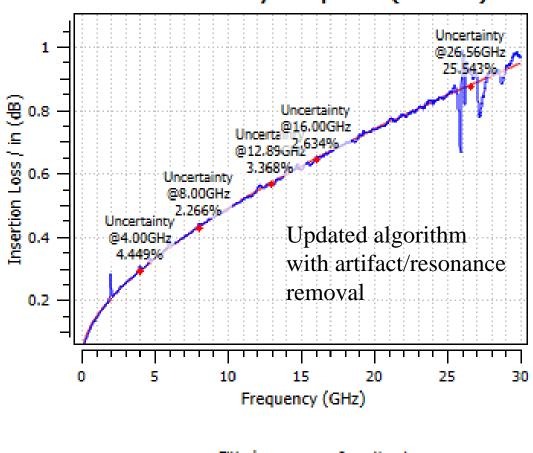

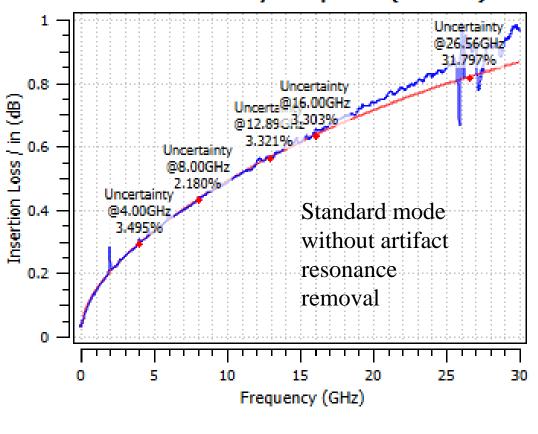

### Case 1 – Delta-L 4.0 with & w/o Resonance/Artifact Removal

Have developed in AITT a curve-fitting routine that eliminates resonance and artifact skewing in the curve fitting

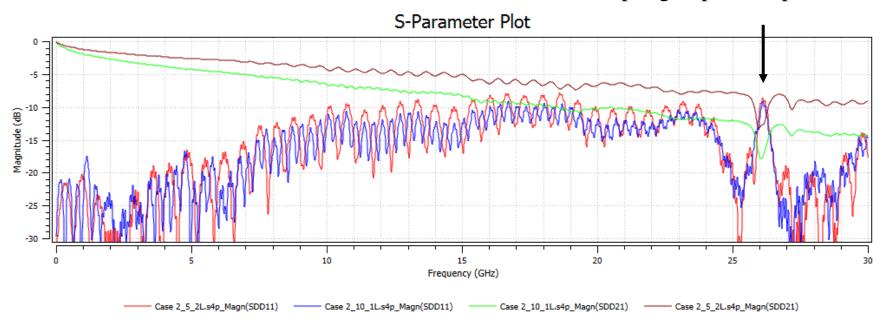

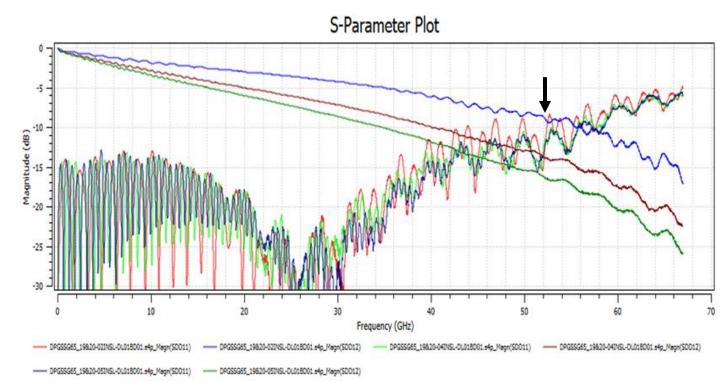

### Case 2 – Coupling to Planes from Via Transition at Feed: S-Parameters

Resonance due to via transition at feed coupling to parallel-plate modes

- Resonance due to via transition coupling to parallel plate modes will result in de-embedding sensitivity

- Crossing of IL and RL in the shorter 2X Thru (brown, red curves) will result in de-embedding sensitivity

- EM simulation can be used here to identify this resonance, its cause, and solution

### Case 2 - TDR

Parallel plate mode coupling to the signal trace is not readily apparent in the TDR

#### Case 2 - Delta-L 4.0 with & w/o Resonance/Artifact Removal

### Uncertainty Report (L1-L2)

Insertion Loss

Fitted Insertion Loss

## Modifying the Curve-Fitting Algorithm

$$W(f) = \left(1 - \left(\frac{f}{f_{max}}\right)\right)^3 \quad (Eq.9)$$

IPC-TM-650TEST METHODS MANUAL, 2.5.5.14

$$W(f) = \left(1 - \left(\frac{f}{f_{max}}\right)\right)^n$$

Allow n = 0, 1, 2, or 3

### Outline

- The Intel Delta-L Methodology

- Test methodology

- Eigenvalue de-embedding

- Curve-fitting insertion loss

- Design and de-embedding essentials for achieving a high-quality outcome at high-frequencies

- Some essentials

- Making accurate S-parameter measurements

- Determining the reference plane for high-quality de-embedding

- causality/passivity

- Mitigating design and layout artifacts in the curve-fitting for IL

- 67 GHz Delta-L

## Summary for Achieving Delta-L to 67 GHz

- 0.5 mm probe pitch, hand-held probes with bases for use in large-volume measurements and in fabrication environment

- Optimized universal footprint to accommodate handheld probes and rapid alignment/placement

- Stripline lengths meet IEEE 370 STD for de-embedding accuracy, e.g., 2" & 5"

#### PacketMicro 0.5 mm GSSG probes

With bases for handheld placement with alignment holes

### **Establishing Best Practices**

- Straight traces (at 67 GHz shorter traces will be necessary anyway and save space) to avoid resonances from serpentine layout

- Universal footprint that ensures good signal return (GND) at the via transition, i.e., well-designed ground return via pattern to avoid coupling to parallel-plate modes

- No via stubs

- Via stitching that is randomized around a nominal spacing

- Careful design with full-wave EM simulation to ensure all of the above

Intel Delta-L 4.0 (0.5 mm pitch)

#### 67 GHz PacketMicro GSSG Probe

#### Probe properties:

- 0.5 mm pitch

- GSSG configuration

- 3-mil robust probe tip

- 47-mi Coaxial cable

- 1.85 mm Samtec connector

- Stainless bases

### 67 GHz Delta-L TV-1

#### 6-layer, Megtron 6, 2", 4", 5" ustrip and stripline

|  | Layer No | LAYER DESCRIPTION                          | Segment | Cu WT(OZ PER SQ FT)   | EST THK (MILS) | Differential<br>(85 Ohms+/-10%) |                  | Dk    | Df    |

|--|----------|--------------------------------------------|---------|-----------------------|----------------|---------------------------------|------------------|-------|-------|

|  |          |                                            |         |                       |                | LW/LS<br>(MILS)                 | Calculated Zdiff | @1GHz | @1GHz |

|  |          | SOLDERMASK                                 |         |                       |                |                                 |                  |       |       |

|  | 1        | TRACE                                      | Cu      | 0.5 + Plating         | 1.6            | 12/5.75                         | 83.45            |       |       |

|  |          |                                            | Prepreg | R-5670G (1078x2)      | 6.68           |                                 |                  | 3.15  | 0.002 |

|  | 2        | GND                                        | Cu      | 1                     | 1.35           | REF                             | REF              |       |       |

|  |          |                                            | Core    | R-5775G               | 11.81          |                                 |                  | 3.45  | 0.002 |

|  | 3        | GND                                        | Cu      | 1                     | 1.35           | REF                             | REF              |       |       |

|  |          |                                            | Prepreg | R-5670G (1080+2116x3) | 17.11          |                                 |                  | 3.58  | 0.002 |

|  | 4        | GND                                        | Cu      | 1                     | 1.35           | REF                             | REF              |       |       |

|  |          |                                            | Core    | R-5775G               | 11.81          |                                 |                  | 3.45  | 0.002 |

|  | 5        | TRACE                                      | Cu      | 1                     | 1.35           | 10/10                           | 85.69            |       | İ     |

|  |          |                                            | Prepreg | R-5670G (1078x2)      | 6.43           |                                 |                  | 3.15  | 0.002 |

|  | 6        | GND                                        | Cu      | 0.5 + Plating         | 1.6            | REF                             | REF              |       |       |

|  |          | SOLDERMASK                                 |         |                       |                |                                 |                  |       |       |

|  |          |                                            |         |                       |                |                                 |                  |       |       |

|  |          | Est Board thickness over conductors (mils) |         |                       | <u>62.44</u>   |                                 |                  |       |       |

|  |          | Meg6                                       |         |                       | mils           |                                 |                  |       |       |

μstrip Layer 1

Stripline Layer 5

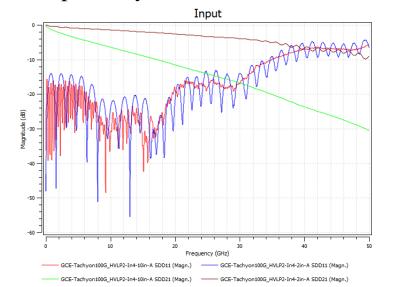

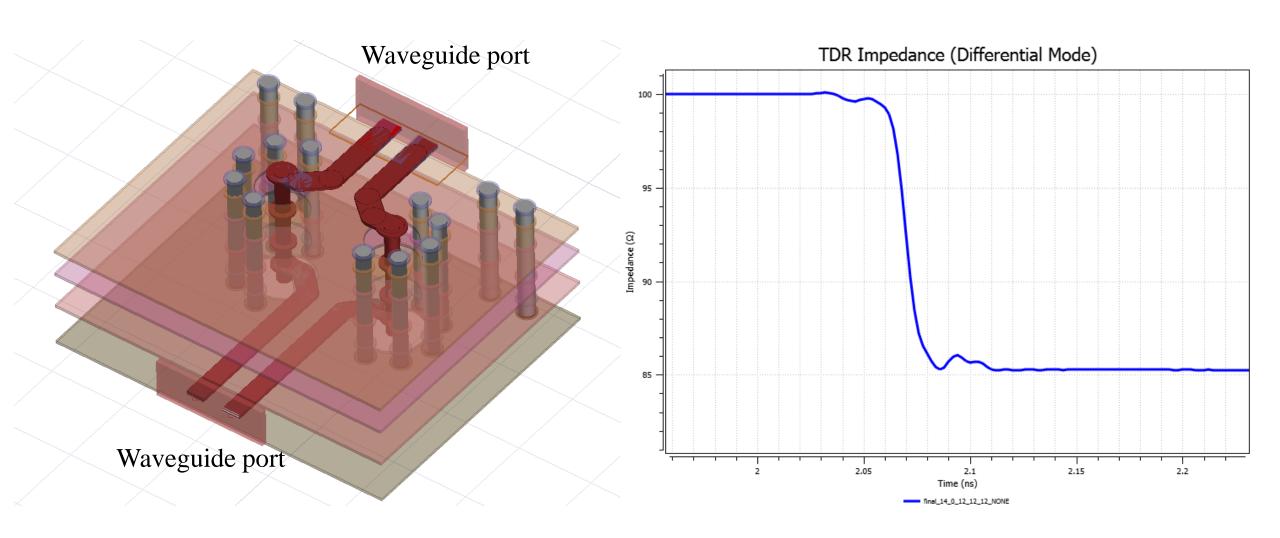

# 67 GHz Delta-L TV-2 Design & EM Modeling

### 67 GHz Delta-L TV-2 – Measured TDR, RL, IL

The IL and RL cross at approximately 52 GHz.

A 2" length for 2X Thru is not necessary, and a shorter length would better satisfy IEEE 370.

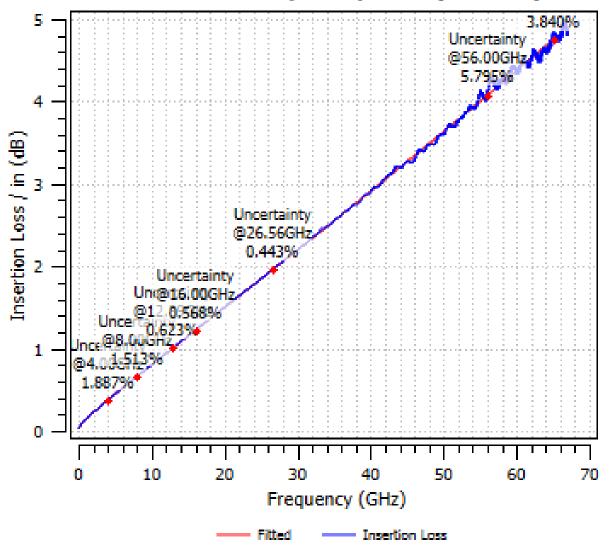

### 67 GHz Delta-L TV-2 – Delta-L Results

### Uncertainty Report (L1-L2)

| Delta-L+ (2L) ₽                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Trace 1                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Input: _19&20-05INSL-DL01BD01.s4p                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Port order: 1→2,, 2N-1→2N                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Trace length: 5.00 in                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Trace 2                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Input: _19&20-02INSL-DL01BD01.s4p                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Port order: 1→2,, 2N-1→2N ×                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Trace length: 3.00 • in                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Options                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| ☐ Enable cut-off freq.: 50 GHz ∨                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Resonance / artifact removal                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| Fitting weight order: 0                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| ▶ Calculate                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Components to Plot                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Magnitude Phase                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| SDD11         SDD12         SDC11         SDC12           SDD21         SDD22         SDC21         SDC22           SCD11         SCD12         SCC11         SCC12           SCD21         SCC22         SCC22         SCC22 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

#### Conclusion

### Achieving a good outcome for Delta-L to 67 GHz will necessitate:

- Robust handheld probe achieved with PacketMicro GSSG

- Excellent design using EM simulation to develop the design

- Probe and footprint optimization work from Delta-L 4.0 Universal Footprint

- Via transition design

- Backdrilling (possibly with air fill, i.e., no plug in the backdrill)

- Per layer optimization

- Material/Dk dependent

- Fabrication/capability dependent

- Fabrication technology HDI (Type 4) vs. PTH (Type 3)

- High-quality S-parameter measurements

### Next Steps

- Clear Signal Solutions/PacketMicro 6-layer, Megtron 6 TV(s)

- Any update to Delta-L 4.0 Universal Footprint

- Via transition optimization for PTH

- Intel higher layer count TV(s)

### Some EM Simulation Tools (incomplete)

- EMCoS Studio (MoM)

- Cadence Clarity (TD-FDTD, FD-FEM)

- CST Studio Suite Dassault Systems (TD-FIT, FD-FEM)

- HFSS Ansys (FD-FEM)

- EMA3D (TD-FDTD)

# Thank you!

# Questions?

(May also send Jim Drewniak questions or request for slides <u>james.drewniak@clearsig.com</u>, put "DesignCon Delta-L slides" in header)